سامسونگ تولید انبوه تراشههای مبتنیبر لیتوگرافی ۳ نانومتری را از هفته آینده آغاز میکند

.jpg)

بهگزارش Yonhap News، انتظار میرود سامسونگ تولید انبوه تراشههای ۳ نانومتری را هفتهی آینده شروع کند. این در حالی است که TSMC، رقیب سامسونگ، تولید تراشههای ۳ نانومتری را از نیمهی دوم سال جاری آغاز خواهد کرد و بدینترتیب، غول فناوری کرهای در این زمینه از رقیب تایوانی خود پیشی خواهد گرفت.

بهگزارش GSMArena، لیتوگرافی ۳ نانومتری سامسونگ درمقایسهبا فرایند ۵ نانومتری این شرکت که در تولید Snapdragon 888 و Exynos 2100 از آن استفاده شده است، ۳۵ درصد مساحت کمتر و ۳۰ درصد عملکرد بهتر و ۵۰ درصد مصرف انرژی بهینهتری خواهد داشت.

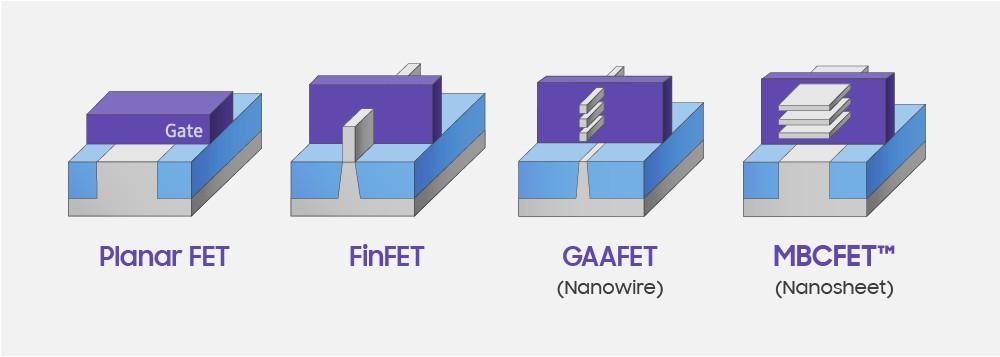

دستیابی به این آمار بهلطف بهرهگرفتن از طراحی موسوم به Gate-All-Around (GAA) در ترانزیستورها بهدست آمده است. درواقع، این فناوری گام بعدی پس از FinFET است؛ زیرا به شرکتهای تراشهسازی اجازه میدهد بدون کاهش توانایی ترانزیستورها در انتقال جریان آنها را کوچک کنند. طراحی GAAFET استفادهشده در لیتوگرافی ۳ نانومتری در تصویر زیر نمایش داده شده است.

جو بایدن، رئیسجمهور ایالات متحده، ماه گذشته از کارخانهی سامسونگ در پیونگتاک بازدید کرد تا در مراسم نمایش فناوری ۳ نانومتری این شرکت حضور یابد. سال گذشته، صحبتهایی مبنیبر این موضوع مطرح شد که این شرکت میتواند ۱۰ میلیارد دلار برای ساخت کارخانهی ریختهگری ۳ نانومتری در تگزاس سرمایهگذاری کند. این سرمایهگذاری اکنون به ۱۷ میلیارد دلار افزایش یافته است و انتظار میرود کارخانهی اشارهشده سال ۲۰۲۴ شروع بهکار کند.

بههرحال، اکنون بزرگترین نگرانی به بازدهی لیتوگرافی جدید سامسونگ مربوط است. این شرکت در اکتبر سال گذشته اعلام کرده است که بازده فرایند ۳ نانومتریاش به سطحی مشابه با فرایند ۴ نانومتری نزدیک میشود.

اگرچه این شرکت در این زمینه هرگز آمار رسمی ارائه نداده است، تحلیلگران معتقدند لیتوگرافی ۴ نانومتری غول فناوری کرهای با مشکلات بازدهی مواجه بوده است. نسل دوم لیتوگرافی ۳ نانومتری در سال ۲۰۲۳ از راه خواهد رسید و نقشهی راه سامسونگ نیز شامل فرایند ۲ نانومتری مبتنیبر MBCFET در سال ۲۰۲۵ است.