بزرگان صنعت ساخت تراشه در حال ایجاد استانداردی جدید برای چیپلتها

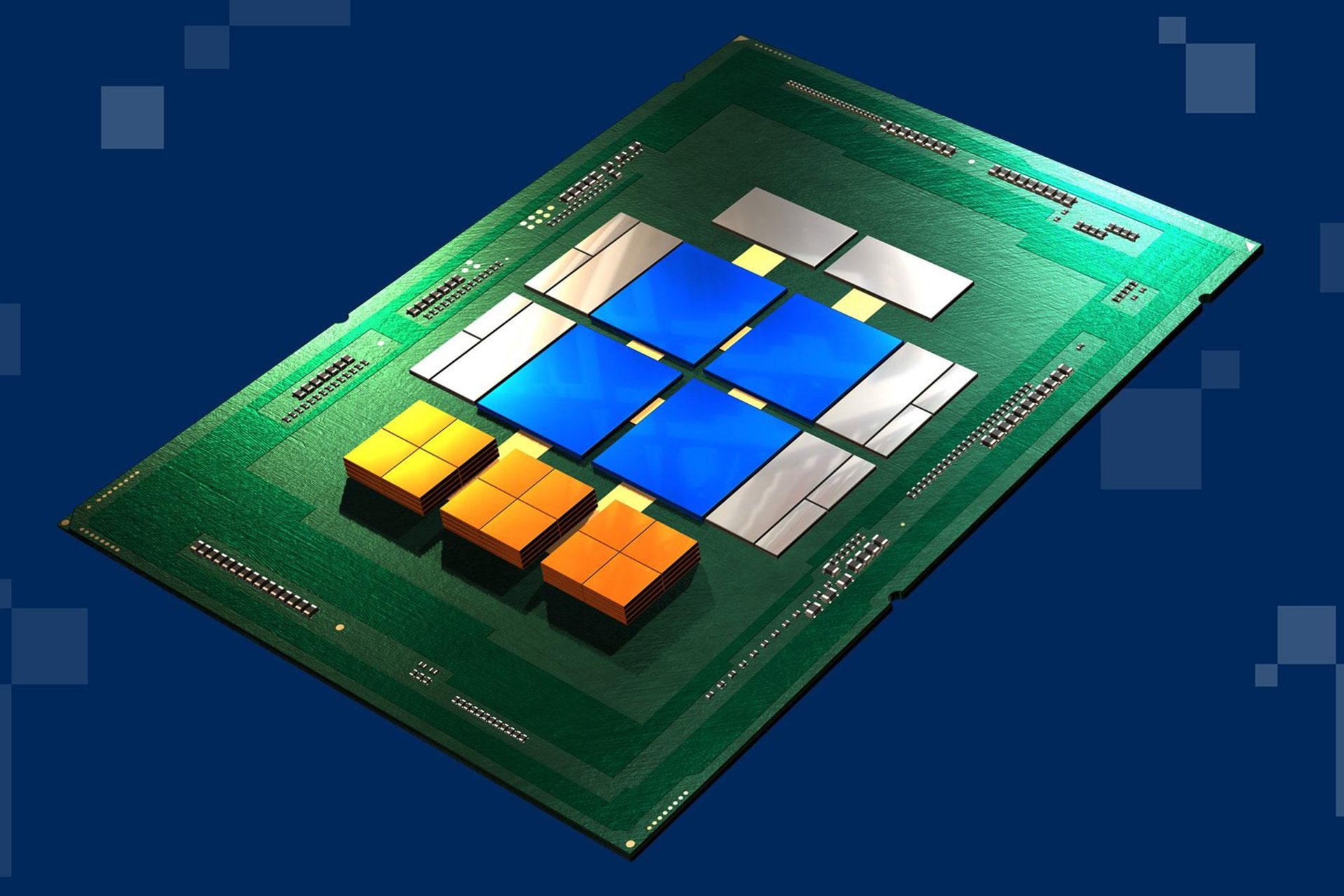

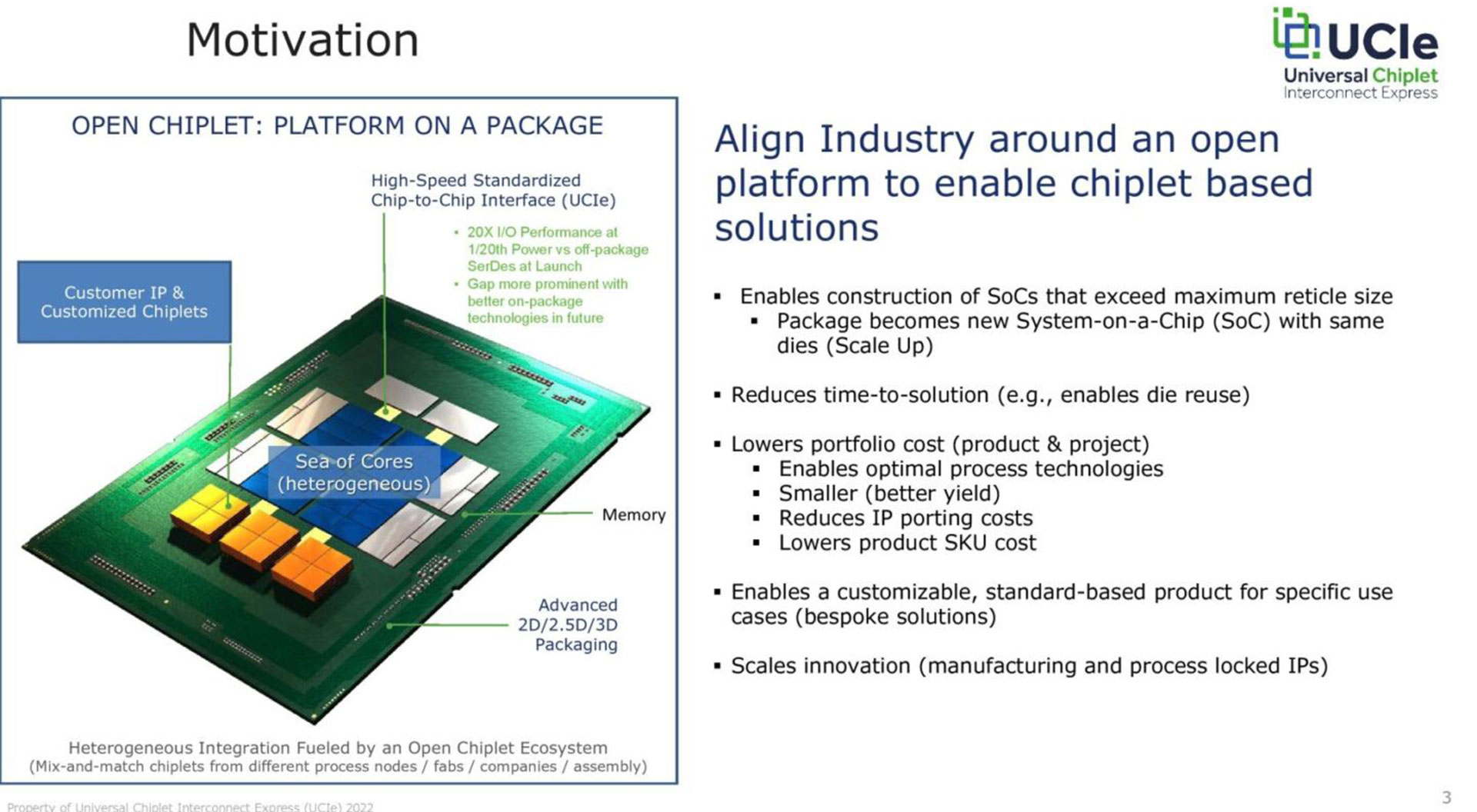

برخی از سازندههای بزرگ سختافزارهای صنعت CPU، ازجمله اینتل، ایامدی، کوالکام، آرم، تیاسامسی و سامسونگ با هدف تعریف استاندارد جدیدی برای طراحیهای پردازندههای مبتنیبر چیپلت (Chiplet) در حال همکاری با یکدیگر هستند. Universal Chiplet Interconnect Express (بهاختصار UCIe) بهدنبال تعریف استاندارد باز و تعاملپذیری برای ترکیب چند قالب سیلیکونی (یا چیپلت) در پکیجی واحد است.

آرستکنیکا مینویسد اینتل و ایامدی و دیگر شرکتها هماکنون بهگونهای در حال طراحی یا فروش پردازندههای مبتنیبر چیپلت هستند. اکثر پردازندههای رایزن از چیپلتها استفاده میکنند و پردازندههای آتی Sapphire Rapids Xeon اینتل نیز چنین وضعیتی دارند؛ اما همه آنها از اتصالات مختلف برای برقراری ارتباط بین تراشهها بهره میبرند. استاندارد UCIe درصورت موفقیت، جایگزین استانداردهای دیگر خواهد شد. ازنظر تئوری، UCIe استفاده از طرحهای مبتنیبر چیپلت را برای شرکتهای کوچکتر آسانتر میکند و میتواند مسیر استفاده از محصولات دیگر شرکتها را هموارتر کند.

طراحیهای مبتنیبر چیپلت هنگام ساخت تراشههای بزرگ پیشرفته سودمند هستند و این مسئله تا حدی بهدلیل کاهش میزان سیلیکونی است که شرکتها به دورریختن آنها مجبور میشوند. اگر نقص تولید روی هسته CPU تأثیر بگذارد، دورریختن چیپلتی ۸ هستهای ارزانتر از قالب پردازندهی بزرگ ۱۶ یا ۳۲ هستهای است.

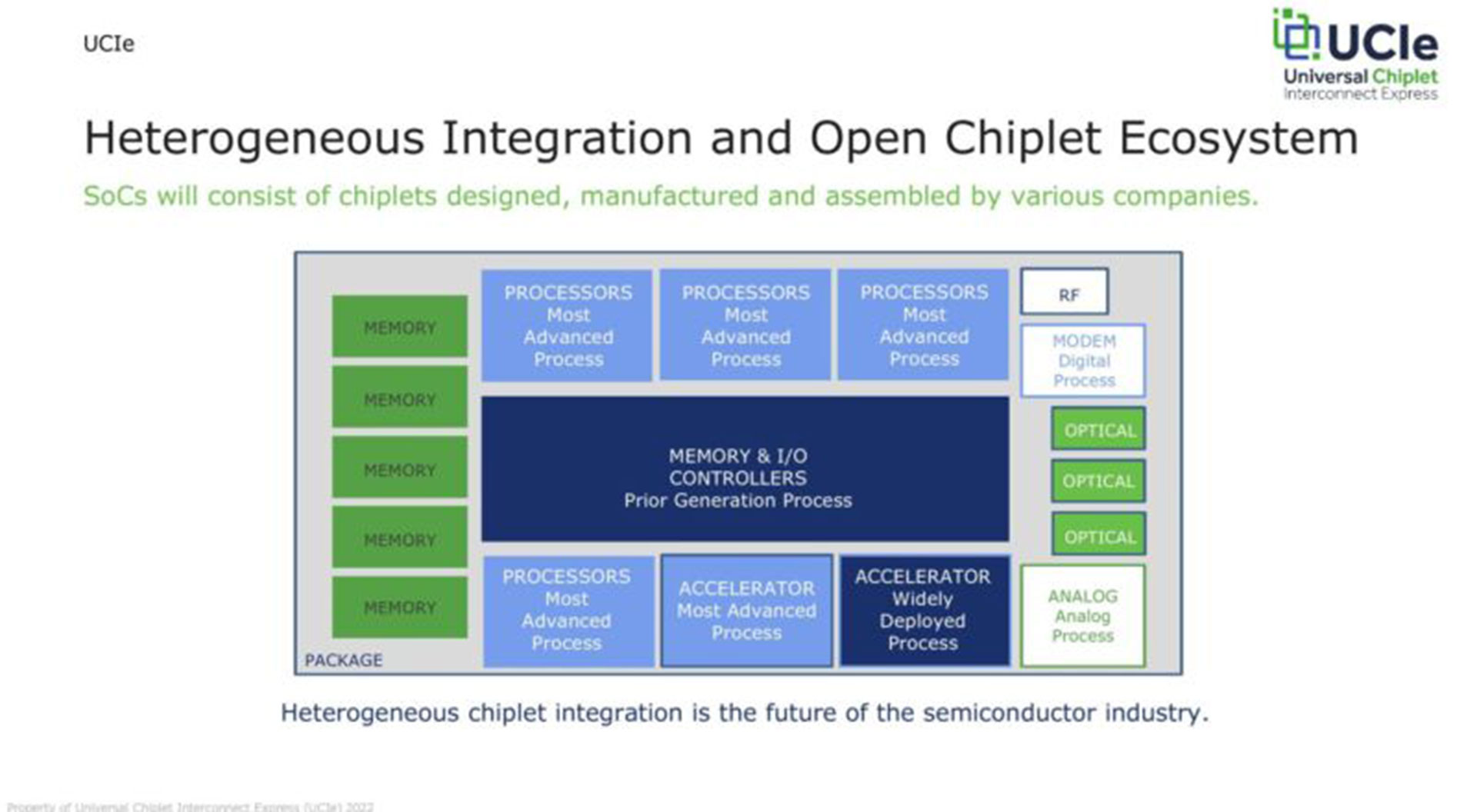

همچنین، استاندارد جدید به شما امکان میدهد تراشهها و فرایندهای تولید را باهم ترکیب کنید. برای مثال، میتوانید از فرایندی قدیمیتر و ارزانتر برای تراشه و فرایندی جدیدتر و پیشرفتهتر برای هستههای پردازنده و حافظه پنهان خود استفاده کنید. حتی قراردادن پردازندهی گرافیکی ایامدی روی همان پکیچ پردازندهی اینتل امکانپذیر میشود.

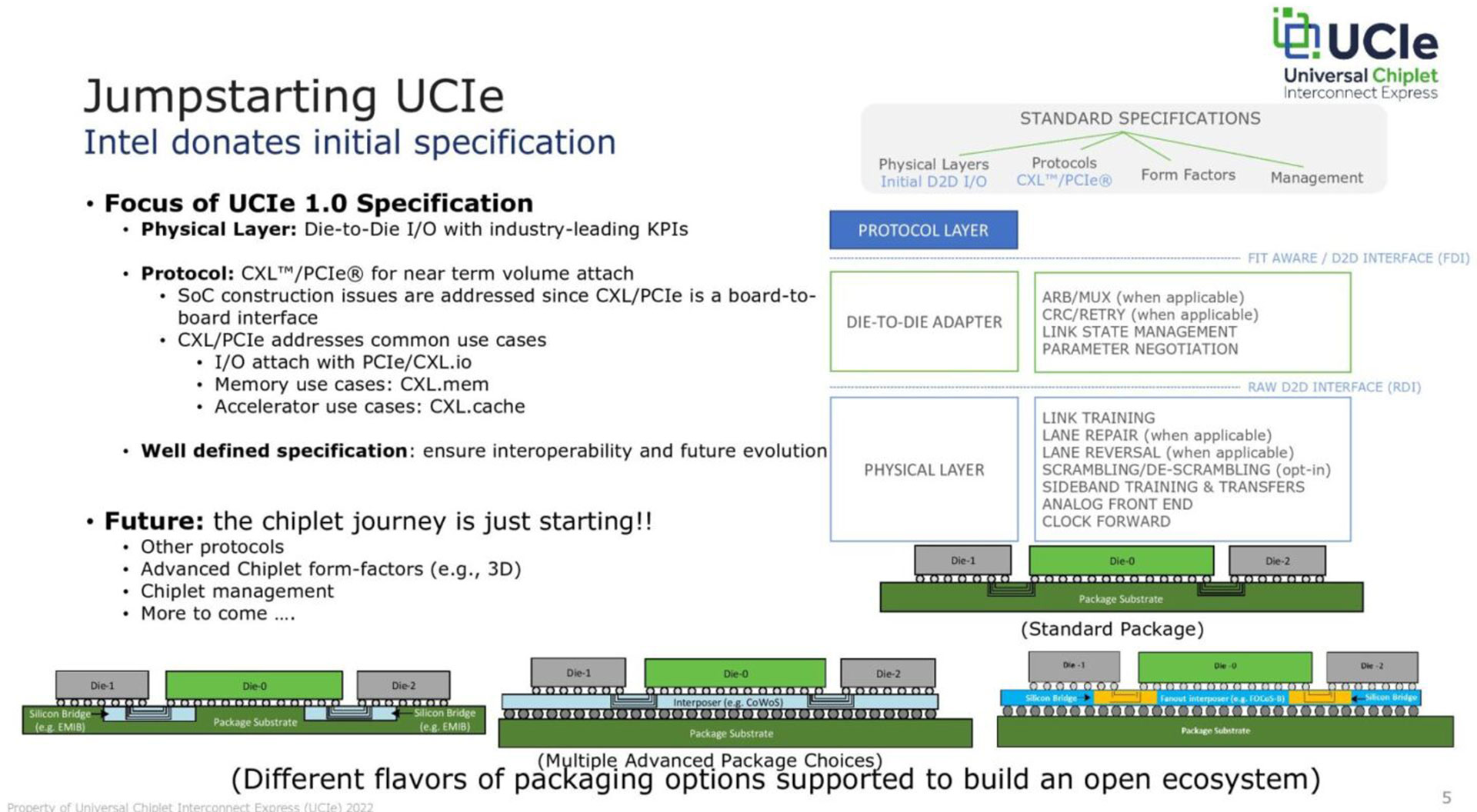

بهگزارش AnandTech، استاندارد UCIe لایههای فیزیکی و پروتکلی طراحی چیپلت را پوشش میدهد. این استاندارد نحوهی اتصال تراشهها به یکدیگر و پروتکلی را برای تسهیل ارتباط بین چیپلتها تعریف میکند؛ اما طراحان آزاد خواهند بود که این تراشهها را به هر شکلی که مناسب میدانند، درکنار یکدیگر قرار دهند.

برای تطبیق با گزینههای مختلف، نسخهی 1.0 UCIe دو سطح عملکرد متفاوت را تعریف میکند. پکیج «استاندارد» به ۱۶ خط داده و ۲۵ میلیمتر فضای بین چیپلتها نیاز دارد؛ درحالیکه پکیج «پیشرفته» از ۶۴ خط داده و فقط ۲ میلیمتر فضا استفاده میکند.

پروتکلهای زیربنایی UCIe از PCI Express و استانداردهای مربوط به Compute Express Link (CXL) تشکیل میشوند که برای سازندگان تراشه آشنا هستند. بااینحال، شرکتهایی که قبلاً پروتکلهای پیشرفتهتر یا خاصتری را برای ارتباطات بین تراشهها توسعه دادهاند، مانند ایامدی و Infinity Fabric، میتوانند از آنها استفاده کنند.

UCIe را در درجهی اول اینتل توسعه داد و سپس به گروه گستردهتر UCIe اهدا شد تا بهعنوان پایهای برای استاندارد جدید عمل کند؛ اما شرکتهای عضو این گروه از اواخر امسال باهم کار روی نسل بعدی فناوری UCIe را آغاز خواهند کرد.