استاندارد PCIe 6.0 برای پیادهسازی در تراشهها آماده شد

نسخهی نهایی مشخصهی PCIe 6.0 تا چند ماه دیگر آماده نمیشود؛ اما پیشنویس نهایی این استاندارد که حدودا پنج ماه پیش منتشر شده است به طراحان تراشه و توسعهدهندگان IP امکان میدهد فرایند پیادهسازی PCIe 6.0 در محصولات را آغاز کنند؛ زیرا هر آنچه در پیشنویس نهایی آمده است در نسخهی نهایی اعمال میشود و شاهد هیچگونه تغییری نخواهیم بود.

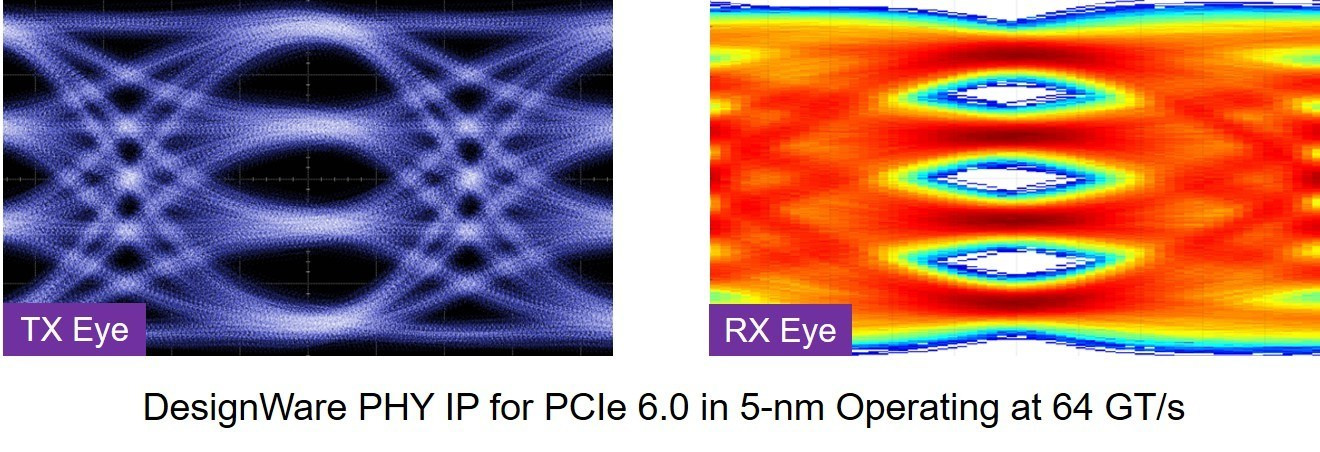

به گزارش تامز هاردور، چند روز پیش شرکت سیناپسیس نخستین راهکار کامل PCIe 6.0 را معرفی کرد تا سازندگان تراشه بتوانند از طریق آن، رابط جدید PCIe 6.0 را در تراشههای متکی بر لیتوگرافی پنج نانومتری بگنجانند. بستهی PCIe 6.0 سیناپسیس که با نام DesignWare شناخته میشود شامل یک کنترلر (با رابط سیناپسیس یا رابطهای اختیاری AMBA 5/4/3 AXI آرم)، رابط فیزیکی (PHY) و IP تأیید اعتبار میشود.

راهکاری که سیناپسیس ارائه میدهد باعث میشود طراحان تراشه بتوانند IP کنترلر و رابط فیزیکی را درون تراشهی پنج نانومتری قرار دهند و سپس با استفاده از IP تأیید اعتبار، بررسی کنند که همهچیز بهدرستی کار میکند یا خیر. از کاربردهای عنوانشده برای استاندارد PCIe 6.0 میتوانیم به مدارهای مجتمع با کاربرد خاص در زمینهی هوش مصنوعی و البته پردازشهای سطح بالا، پردازندههای گرافیکی، کنترلرهای SSD و... اشاره کنیم.

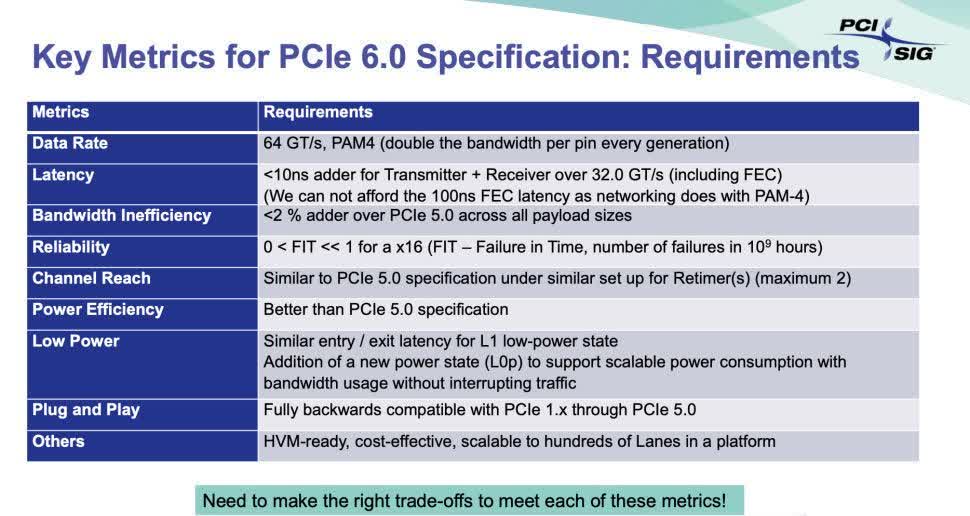

مبحثی که در PCIe 6.0 اهمیت پیدا میکند، پهنای باند است. اطلاعات رسمی از پهنای باند حداکثر ۱۲۸ گیگابایت بر ثانیه از طریق یک رابط x16 در هر جهت خبر میدهند. این یعنی از لحاظ تئوری راهکارهای مبتنی بر PCIe 6.0 میتوانند دادهها را با سرعت ۲۵۶ گیگابایت بر ثانیه انتقال بدهند؛ عددی که شاید در نگاه اول باورکردنی نباشد.

کنترلر ارائهشده توسط سیناپسیس از نرخ انتقال دادهی حداکثر ۶۴ گیگاترنسفر بر ثانیه به ازای هر پین پشتیبانی میکند. این عدد برای PCIe 5.0 و PCIe 4.0 بهترتیب ۳۲ و ۱۶ گیگاترنسفر بر ثانیه به ازای پین بود. مشخصهی PCIe 6.0 همچنین از سیگنالدهی PAM4، تصحیح مستقیم خطا با تأخیر پایین، حالت FLIT و حالت L0p پشتیبانی میکند؛ تمامی این موارد، قابلیتهای کلیدی PCIe 6.0 محسوب میشوند. در کنار اینها، کنترلر سیناپسیس از الگوریتمهای اختصاصی DSP این شرکت پشتیبانی میکند. این الگوریتمها میتوانند فرایند برابرسازی آنالوگ و دیجیتال را بهینه کنند تا میزان مصرف انرژی ۲۰ درصد کاهش پیدا کند.

مقالههای مرتبط:

سیناپسیس میگوید معماری کنترلر PCIe 6.0 و رابط فیزیکی در دستهی معماریهای آگاه از ترتیب قرار میگیرد تا ارتباط متقابل بین بستهها به هنگام انتقال داده با سرعت بالا، به حداقل برسد. افزون بر اینها سیناپسیس ادعا میکند از مسیر دادهی بهینهشده استفاده کرده است تا از ارائهی تأخیر بسیار کم اطمینان حاصل کند.

جان کوئتر، قائممقام واحد بازاریابی و استراتژی IP در سیناپسیس، میگوید رایانش ابری پیشرفته، ذخیرهسازی داده و فناوری یادگیری ماشین حجم زیادی از داده را منتقل میکنند و به همین دلیل تولیدکنندگان باید برای فراهمسازی پهنای باند مورد نیاز همواره سراغ جدیدترین رابطها بروند که سرعت بالایی دارند و تأخیرشان کم است.

در نظر داشته باشید که زمان زیادی باقی مانده است تا محصولات متکی بر PCI-e 6.0 در بازار عرضه شوند. طی ۱۸ ماه اخیر برای نخستین بار شاهد عرضهی پردازندههای گرافیکی و درایوهای SSD M.2 با رابط PCIe 4.0 بودیم؛ انویدیا چند ماه پیش از طریق پردازندههای گرافیکی خانوادهی امپر پشتیبانی از PCIe 4.0 را آغاز کرد.

در آینده رابط PCIe 5.0 نیز در قالب پردازندههای گرافیکی و SSD-ها و مادربردها از راه میرسد. تفاوت چشمگیر در عملکرد رابط PCIe 6.0 نسبت به نسخههای قبلی، در مصارف دیتاسنتر به چشم میآید و شاید برای کاربران عادی چندان مهم نباشد. احتمالا کاربران بهاینزودی به سرعت بسیار زیادی که PCIe 6.0 ارائه میدهد نیاز پیدا نخواهند کرد.