TSMC جزئیات فرایند تولید سه نانومتری را منتشر کرد؛ تولید انبوه در نیمه دوم ۲۰۲۲

شرکت تایوانی TSMC در رویداد سالانهی اخیر خود، Technology Symposium، مشخصات فرایند تولید سه نانومتری را شرح داد. در رویداد اخیر، جزئیات طراحی و نقشهی راه فرایند سه نانومتری شرح داده شد. همچنین مهندسان غول دنیای تراشه، جزئیات روشهای تولیدی جایگزین پنج نانومتری یعنی N5P و N4 را هم توضیح دادند.

اولین اطلاعات مهم رویداد TSMC به فرایند تولید N5 اختصاص داشت که از نسل دوم فرایندهای تولیدی DUV و EUV در آن استفاده میشود. این فرایند تولیدی پس از +N7 که استفادهی زیادی در صنعت نداشت، با روشهای جدید سعی در بهبود کارایی تراشهها دارد. پردازندهی Kirin 990 تنها پردازندهای بود که از روش تولید +N7 بهره میبرد. بههرحال روش تولید N5 یا همان پنج نانومتری از مدتها پیش وارد فرایند تولید انبوه شده است و اولین تراشههای مبتنی بر آن، به دست مشتریان میرسند. کارشناسان پیشبینی میکنند که اولین محصولات مصرفی مجهز به پردازندههای پنج نانومتری هم در سال جاری به بازار عرضه شوند. شایعههای متعدد مدعی هستند که نسل بعدی پردازندههای اختصاصی اپل، با استفاده از تراشههای پنج نانومتری تولید میشوند.

TSMC ادعا میکند که فرایند تولید پنج نانومتری ازلحاظ سرعت پیشرفت در مسیر بهتری نسبت به نسلهای قبلی قرار دارد. آنها میگویند N5 در مقایسه به N7 یک فصل زودتر به بازدهی مناسب تولید رسید. تراشههای پنج نانومتری اکنون در وضعیت تولید انبوه، بازدهی بسیار بیشتری نسبت به هر دو نسل قبلی یعنی N7 و N10 دارند. مسیر پیشرفت تولید و کاهش عیوب آن نیز با سرعتی بالاتر نسبت به مسیر پیشرفت روشهای قبلی طی میشود.

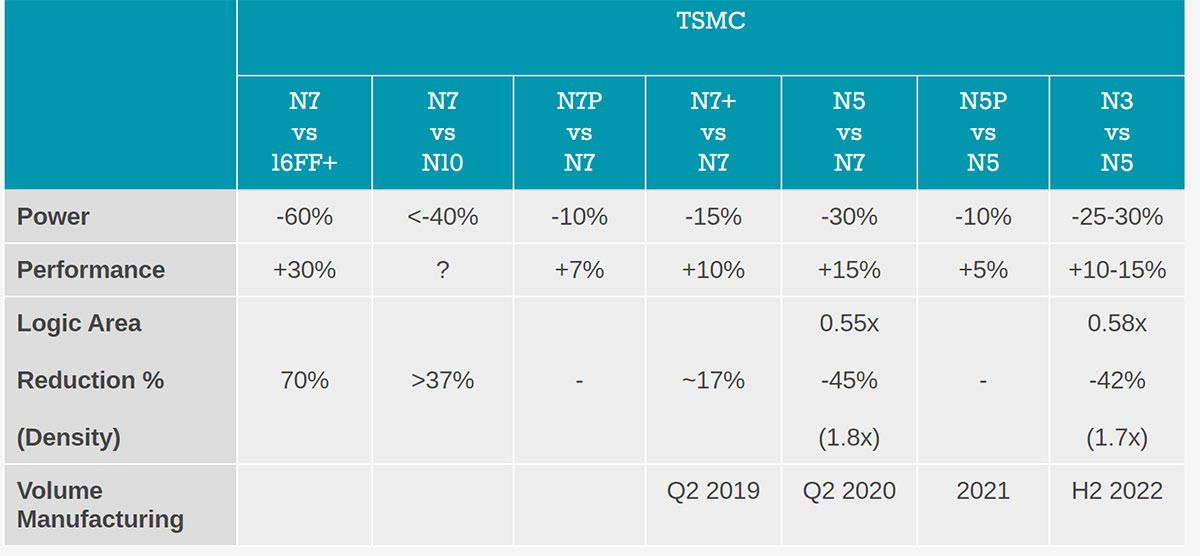

غول تایوانی دنیای نیمههادی روش تولید جدیدی بهنام N5P را در دستور کار دارد که براساس فناوری کنونی N5 توسعه مییابد. هدف از معرفی روش بهینهی جدید، بهبود کارایی و مصرف توان با استفاده از طراحی قبلی است. مهندسان ادعا میکنند که روش بهینه، پنج درصد سرعت بیشتر و ۱۰ درصد مصرف توان پایینتر دارد.

TSMC علاوه بر N5P روش دیگری بهنام N4 را نیز توسعه میدهد. روش مذکور، بهینهسازی را در سطوح عمیقتری مبتنی بر روش تولید پنج نانومتری در پیش میگیرد. از جزئیات مهم N4 میتوان به استفاده از لایههای EUV بیشتر اشاره کرد. همچنین طراحان تراشه برای ورود به روش تولید بهینه نیاز به تغییرات و پیادهسازی ساختارهای آنچنان جدیدی نخواهند داشت. تولید آزمایشی N4 در فصل چهارم سال ۲۰۲۱ شروع میشود و تولید انبوه هم برای سال ۲۰۲۲ برنامهریزی شده است.

مهمترین خبر TSMC در رویداد اخیر، مربوط به مرحلهی مهم بعدی در عبور از فرایند تولید پنج نانومتری بود. آنها طراحی و تولید براساس نسل بعدی یعنی سه نانومتری را با جدیت دنبال میکنند. اولین اخبار پیرامون برنامهی طراحی و توسعهی روش تولید سه نانومتری، سال گذشته از TSMC منتشر شد و امیدها را برای عرضهی محصولات مبتنی بر روش جدید، بیشتر کرد.

مقالههای مرتبط:

سامسونگ هم مانند TSMC فرایند تولید سه نانومتری را در برنامهی طراحی و آزمایش دارد. کرهایها از ساختار ترانزیستوری GAA برای تولید استفاده میکنند، درحالیکه TSMC هنوز به ترانزیستورهای FinFET وفادار خواهند ماند. آنها امیدوار هستند که FinFET در روش تولید نسل بعدی هم دستاوردهای خوبی برای عبور از هر نسل روش تولید، بههمراه داشته باشد.

روش تولید سه نانومتری، برخلاف پنج نانومتری با بهبود قابلتوجه کارایی و صرفهجویی در مصرف توان همراه میشود. شرکت تایوانی ادعا میکند که N3 با بهبود کارایی به میزان ۱۰ تا ۱۵ درصد در مصرف توان مساوی یا بهبود مصرف توان به میزان ۲۵ تا ۳۰ درصد در سرعت برابر همراه میشود. آنها همچنین ادعا میکنند که چگالی فضای بخشهای منطقی تراشه هم بهبود ۱/۷ برابری را تجربه کند. به بیان دیگر، در بخش منطقی تراشهی N3 به N5 شاهد فاکتور مقیاسدهی 0.58x خواهیم بود. البته کوچک شدن فضا در تمامی ساختارهای تراشهای به یک میزان پیشبینی نمیشود. چگالی SRAM احتمالا ۲۰ درصد بهبود خواهد داشت که فاکتور مقایسدهی 0.8x را نشان میدهد. درمقابل، ساختارهای آنالوگی وضعیت بدتری دارند و حتی مقیاس 1.1x برای چگالی آنها پیشبینی میشود.

طراحی تراشههای مدرن، بیش از همیشه روی SRAM تمرکز میکند. بهصورت کلی، نسبت ۷۰ به ۳۰ برای چگالی بخش SRAM نسبت به بخش منظقی (Logic) در هر تراشه پیشبینی میشود. درنتیجه در سطح تراشه، پیشبینی کوچک شدن قالب حدود ۲۶ درصد یا کمتر خواهد بود.

تولید اولیه و آزمایشی N3 در سال ۲۰۲۱ شروع میشود و TSMC، تولید انبوه را برای نیمهی دوم ۲۰۲۲ پیشبینی کرده است. جزئیاتی که شرکت تایوانی پیرامون مصرف توان و قدرت در فرایند تولید سه نانومتری منتشر کرد، شباهت زیادی به جزئیات فرایند 3GAE سامسونگ دارد. ازطرفی چگالی در روش تولید TSMC بسیار بیشتر پیشبینی میشود. درنهایت باید منتظر ماهها و سالهای پیشرو باشیم تا فرایندهای تولید در ابعاد بسیار کوچکتر، بهمرور از حالت آزمایشی به تولید انبوه برسند و شاید تأثیری عمیق بر افزایش کارایی پردازندهها داشته باشند.