نخستین جزئیات معماری گرافیکی بعدی انویدیا با نام Lovelace فاش شد

براساس ادعاهای افشاگری که مدتها پیش تقریبا تمامی اطلاعات معماری گرافیکی امپر (Ampere) انویدیا را فاش کرد، تیم سبز از مدتی پیش کار روی معماری بعدی خود را برای کارتهای گرافیک آغاز کرده hsj و از نام ایدا لاولیس ریاضیدان برای آن استفاده خواهد کرد. در همین حین، بهنظر میرسد تکمیل توسعهی معماری هاپر (Hopper) فعلا تا تاریخی نامشخص بهتأخیر افتاده و احتمالا معماری لاولیس قرار است جای هاپر را بگیرد. یکی از مشخصههای lil معماری هاپر ساختاری بهنام MCM یا Multi-Chip-Module است. در این نوع ساختار، چند تراشه در یک بستهی پردازشی قرار میگیرند.

انویدیا همواره از نام افراد برجسته برای معماریهای گرافیکی خود استفاده میکند. بهعقیدهی بسیاری از تاریخدانان، ایدا لاولیس نخستین طرفدار جدی کامپیوترها و نخستین فردی بود که فهمید موتور تحلیلی (Analytical Engine) افزونبر محاسبات محض، کاربردهای دیگری نیز دارد. ناگفته نماند نخستینبار طرح موتور تحلیلی را چارلز ببیج ارائه داد. همچنین، لاولیس نخستین الگوریتمی را ارائه داد که قرار بود دستگاهی نظیر موتور تحلیلی چارلز ببیج براساسش کار کند. تمامی این اتفاقات تقریبا نیم قرن پیش از آن رخ داد که آلن تورینگ کارش را بهاتمام برساند و کامپیوترهای همهمنظوره را در بحبوحهی جنگ جهانی طراحی کند.

همانطورکه اشاره کردیم، انویدیا علاقهی فراوانی به استفاده از نام دانشمندان و ریاضیدانان و فیزیکدانان برجسته برای معماریهای گرافیکیاش دارد و معماری جدید این شرکت با نام لاولیس، از این قاعده مستنثی نیست. خبرگزاری Videocardz میگوید به مدارکی در فروشگاه انویدیا دست یافته است که نشان میدهد شایعهها با محوریت انتخاب لاولیس بهعنوان نام نسل بعد معماری گرافیکی تیم سبز حقیقت دارد.

اگر نگاهی به تصویری بیندازید که انویدیا در مراسم GTC 2018 منتشر کرد، نهتنها نام ایدا لاولیس، بلکه نامهای دیگری را میبینید که احتمالا قرار است بهعنوان نام معماریهای نسل بعد انویدیا انتخاب شوند. این یعنی احتمالا جن سون هوانگ، مدیرعامل انویدیا، نام تمامی معماریهای آیندهی شرکتش را غیرمستقیم در نطق اصلی کنفرانس GTV 2018 اعلام کرده است.

چندین خبرگزاری بهنقل از منابعی که خواستهاند ناشناس بمانند، مدعی شدهاند لاولیس قرار است برپایهی لیتوگرافی پنجنانومتری ساخته شود. ازآنجاکه انویدیا وظیفهی تولید تراشههای گرافیکیاش را برعهدهی سامسونگ گذاشته، درحالحاضر نمیدانیم لیتوگرافی پنجنانومتری معماری لاولیس متعلق به TSMC است یا سامسونگ.

فراموش نکنید طبق گزارش جدیدی که مدتی پیش از کرهجنوبی منتشر شد، انویدیا سفارش تولید تراشههای ششنانومتری را ثبت کرده است. این یعنی یا پیش از رویکارآمدن لاولیس انویدیا معماری دیگری با لیتوگرافی ششنانومتری معرفی میکند یا لاولیس قرار است برپایهی لیتوگرافی ششنانومتری ساخته شود. حساب کاربری Kopite در توییتر سابقهی افشای اطلاعات دقیق بسیار زیادی از معماری امپر دارد. او ادعا میکند لاولیس متکی بر لیتوگرافی پنجنانومتری است.

Kopite اعلام کرده است که معماریهای هاپر و کارتهای گرافیک مبتنیبر سبک طراحی MCM فعلا تأخیر خوردهاند. این خبر برای علاقهمندان به دنیای فناوری قطعا خوشحالکننده نخواهد بود؛ زیرا پردازندهای گرافیکی مجهز به سبک طراحی MCM قدرت پردازشی بیشتری از پردازندههای گرافیکی امروزی ارائه میدهد و میتواند رکوردهایی را جابهجا کند. اگر همچنان قرار است به طراحیهای یکپارچه وابسته باشیم، بازده تراشهها قرار است همچنان مشکلی جدی باشد.

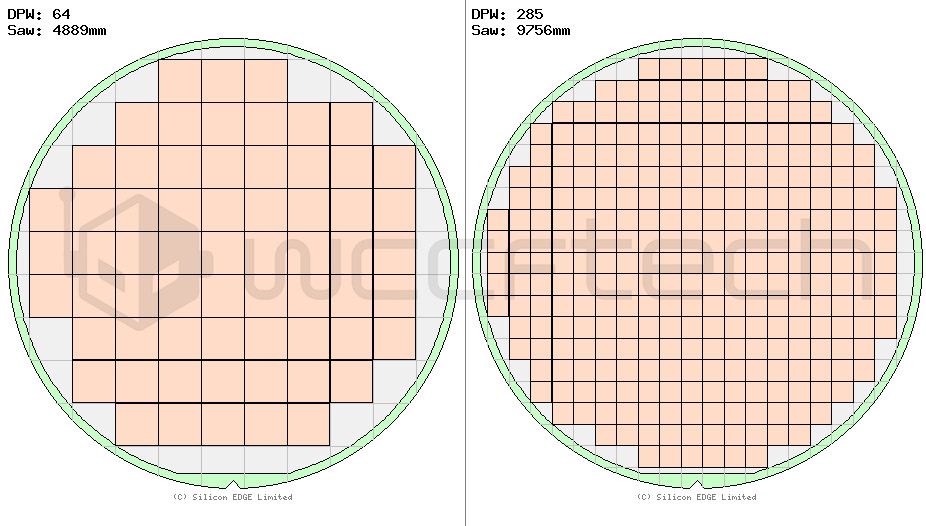

برای فهم بهتر وضعیت، بهتر است محاسباتی انجام دهیم. تراشهای را در نظر بگیرید که مساحتش به ۴۸۴ میلیمترمربع میرسد (تراشهای همچون وگا ۶۴). ابعاد این تراشه ۲۲ در ۲۲ میلیمتر است. تقسیم این تراشهی یکپارچه به چهار تراشهای که ابعادشان معادل ۱۱ در ۱۱ میلیمتر است، باعث میشود به همان میزان سطح دسترسی پیدا کنید (۴۸۴ میلیمترمربع) و درنهایت، بازده نیز افزایش یابد.

شاید از خود بپرسید چگونه؟ براساس تخمینها، ویفری ۳۰۰ میلیمتری باید بتواند ۱۱۴ تراشهی یکپارچه (۲۲ در ۲۲) یا ۴۹۱ تراشهی کوچکتر (۱۱ در ۱۱) را بسازد. ازآنجاکه در روش دوم برای ایجاد تراشهای یکپارچه به چهار تراشهی کوچکتر نیاز داریم، درنهایت، با ۱۲۲ تراشهی ۴۸۴ میلیمترمربعی MCM سروکار خواهیم داشت. همین موضوع بهمعنای ۷٫۶ درصد افزایش بازده است.

وقتی بحث به تراشههای بزرگتر میرسد، میزان افزایش بازده نیز بیشتر میشود. نهایت تکنیکهای لیتوگرافی با بازدهی معقول تقریبا ۸۱۵ میلیمترمربع است؛ پس روی تراشهای ۳۰۰ میلیمتری میتوانیم تقریبا ۶۴ عدد از این تراشهها (۲۸٫۵۵ در ۲۸٫۵۵) یا ۲۸۵ تراشهی کوچکتر (۱۴٫۲۷ در ۱۴٫۲۷) را جای دهیم. در چنین تراشهای، مجموعا به ۷۱ تراشهی مبتنیبر طراحی MCM میرسیم که با افزایش تقریبا ۱۱ درصدی بازده همراه است.

اعدادی که به آنها اشاره کردیم، براساس برخی تخمینها مطرح شدهاند و با استفاده از محاسباتی ناقص بهدست آمدهاند؛ زیرا در محاسباتمان، عوامل مهمی نظیر میزان بازدهی تکنیکهای پکیجینگ و مشخصههای تراشههای مستطیلشکل و بهینهسازیهای دیگر را وارد معادله نکردهایم که مبتنیبر شکل ویفر هستند.

مقالههای مرتبط:

بااینحال، همان اعداد میتوانند دیدی کلی به ماجرا به ما بدهند. همچنین، محاسبات ما عوامل دیگری مثل افزایش سود ازطریق کاهش ضایعات را شامل نمیشود. تراشهی معیوب ۸۱۵ میلیمترمربعی ضایعات بسیار بیشتری از تراشهی ۲۰۳ میلیمترمربعی دارد.

درهرصورت فعلا بهجز کدنام و لیتوگرافی، اطلاعات زیادی از معماری لاولیس انویدیا نمیدانیم؛ بااینحال در آیندهای نهچندان دور، قطعا اطلاعات بیشتری دربارهی آن خواهیم شنید.